Software se hace cargo del manejo de caché en memoria multi-núcleo: MIT

En las computadoras actuales, mover información hacia y desde la memoria principal consume tal cantidad de tiempo y energía que los microprocesadores tienen sus propios bancos de memoria de alta velocidad, conocidos como “memoria caché”, para almacenar información utilizada de manera frecuente.

La administración del caché ha requerido de manera tradicional algoritmos bastante simples que pueden ser programados dentro del mismo chip. Sin embargo, para cubrir las expectativas de crecimiento sostenido del poder computacional, los fabricantes de chips han equipado sus chips con más y más cores (núcleos o unidades de procesamiento). Y a medida que los cores proliferan, la administración de la memoria caché se hace más y más difícil.

Cómo resolver el enigma multi-núcleos

Daniel Sánchez, profesor asistente del MIT, considera que es hora de que la administración del caché sea realizada con software. Esta semana, en la Conferencia Internacional Sobre Arquitecturas Paralelas y Técnicas de Compilación, Sánchez y su estudiante Nathan Beckmann presentaron un nuevo sistema al que denominaron Jigsaw, que vigila los cálculos que se están realizando en un chip multi-núcleo y administra la memoria caché de acuerdo a esos requerimientos.

Acelerando los cálculos en chips multi-núcleos

En experimentos de simulación donde se ejecutaban cientos de aplicaciones en chips multi-núcleos de 16 y 64 cores, Sánchez y Beckmann hallaron que Jigsaw podía acelerar la ejecución en un promedio de 18 por ciento –con el doble de mejora en algunos casos– al tiempo que reducía el consumo de energía hasta en un 72 por ciento. Sánchez considera que las mejoras en rendimiento que ofrece Jigsaw podrían incrementarse a medida que aumenta el número de núcleos o cores.

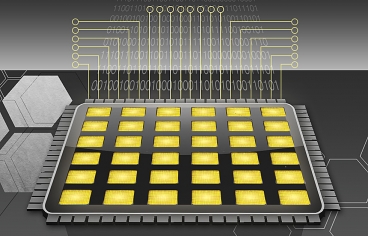

En la mayoría de chips multi-núcleos, cada núcleo tiene cachés pequeñas propias. Pero también está lo que se conoce como caché de último nivel, que se comparte por todos los núcleos. “Ese caché es casi del 40 al 60 por ciento del chip en su totalidad”, dice Sánchez. “Es una fracción significativa del área que resulta crucial para el rendimiento. Si no tuviéramos es caché, algunas aplicaciones serían un nivel de magnitud más lentas”.

Físicamente, el último nivel de caché se divide en bancos de memoria independientes y distribuidos en todo el chip; para cualquier core, el acceso al banco de memoria caché más cercano toma menos tiempo y consume menos energía que accesar uno más alejado. Sin embargo, el último nivel de caché es compartido por todos los núcleos y la mayoría de chips asignan aleatoriamente datos a los bancos de memoria.

Jigsaw, en contraste, vigila qué núcleos acceden a qué información de manera más frecuente y calcula la mejor y más eficiente distribución de información en los bancos de caché. Por ejemplo, la información utilizada exclusivamente por un núcleo específico se almacena cerca de ese núcleo, mientras que información accesada en frecuencias similares por todos los núcleos se almacena cerca del centro del chip, minimizando la distancia promedio que la información debe viajar.

Jigsaw también varía la cantidad de espacio de memoria caché asignada para cada tipo de datos, dependiendo de la manera en que se accesa. La información reutilizada frecuentemente recibe más espacio que la información reutilizada de manera poco frecuente o sólo utilizada una vez.

En principio, la optimización del espacio de caché asignado requiere la evaluación de cómo el chip como un todo se comportará dada cada posible asignación de memoria caché a todos los cálculos ejecutados por todos los núcleos. Esta evaluación tomaría mucho tiempo, pero al ignorar algunos escenarios particulares que serían poco probables en la práctica, Sánchez y Beckmann pudieron desarrollar un algoritmo aproximado de optimización que corre eficientemente aún a medida que la cantidad de núcleos y distintos tipos de datos aumentan dramáticamente.

Por supuesto, debido a que la optimización se basa en las observaciones que Jigsaw realiza de las actividades del chip, “es lo más óptimo por realizar, ya que los programas se comportarán en los siguientes 20 milisegundos de la manera en que lo hicieron en los últimos 20 milisegundos”, dijo Sánchez. “Sin embargo, existe fuerte evidencia experimental que los programas típicamente tienen fases estables de cientos de milisegundos, o incluso segundos”.

“Más y más cálculos se están realizando en los centros de datos”, dijo Jason Mars, profesor de la Universidad de Michigan. “En el espacio del centro de datos (datacenter), será muy importante poder tener particiones de microarquitectura y recursos asignados en base a los requerimientos de cada aplicación”.

“Cuando tienes múltiples aplicaciones ejecutándose en un sólo equipo” explica, “existe un punto de interferencia donde las tareas pueden dañar su rendimiento entre sí. Con el actual hardware, existe un número limitado de mecanismos para administrar la manera en que interfieren las tareas entre sí”.

Mars dice que un sistema como Jigsaw proporciona una capa de abstracción entre el hardware del chip y el software que ejecuta. “Empresas como Intel, una vez expongan las configuraciones de microarquitectura a través de la capa de software, deben conservar esa interfase para futuras generaciones del procesador”, dice Mars. “Si Intel desea hacer algo audaz con la microarquitectura para realizar un gran cambio, deberán conservar el soporte, lo que puede limitar las opciones de diseño que pueden explorar”.

“Sin embargo” añade, “las técnicas en Jigsaw parecer ser muy prácticas, y podría vislumbrar algunas variantes de esta interfase hardware-software que sea incorporada en diseños futuros. En realidad, es un método muy atractivo”.

Más información aquí.

Comentarios